Fused all-gather+GEMM HBM-buffer kernel for iris.ops#346

Fused all-gather+GEMM HBM-buffer kernel for iris.ops#346

Conversation

…yaswann/iris_xops_perf

…yaswann/iris_xops_perf

…yaswann/iris_xops_perf

…yaswann/iris_xops_perf

…yaswann/iris_xops_perf

|

@copilot Cherry-pick the config files from my fork: Bring in the changes for the auto config only. The major changes are in :

Don't touch After porting, run benchmark/ops/bench_all_gather_matmul.py on MI355X and MI300X for all sizes which configs were added for. Produce a bar plot for each GPU showing |

…ops-perf Cherry-picked: - benchmark/ops/all_gather_matmul/auto_config.py — auto-selection of kernel configs - benchmark/ops/all_gather_matmul/configs/ — all JSON configs for mi300x and mi355x - benchmark/ops/bench_all_gather_matmul.py — updated to use auto-config iris/ops/__init__.py and tests/ops/ left untouched. Agent-Logs-Url: https://github.com/ROCm/iris/sessions/e61a7d71-7247-4dfb-907e-37befa0bbf63 Co-authored-by: ryanswann-amd <109695074+ryanswann-amd@users.noreply.github.com>

Agent-Logs-Url: https://github.com/ROCm/iris/sessions/e61a7d71-7247-4dfb-907e-37befa0bbf63 Co-authored-by: ryanswann-amd <109695074+ryanswann-amd@users.noreply.github.com>

Agent-Logs-Url: https://github.com/ROCm/iris/sessions/e61a7d71-7247-4dfb-907e-37befa0bbf63 Co-authored-by: ryanswann-amd <109695074+ryanswann-amd@users.noreply.github.com>

Ported in commits ef0a173 and caed8a5. Cherry-picked from

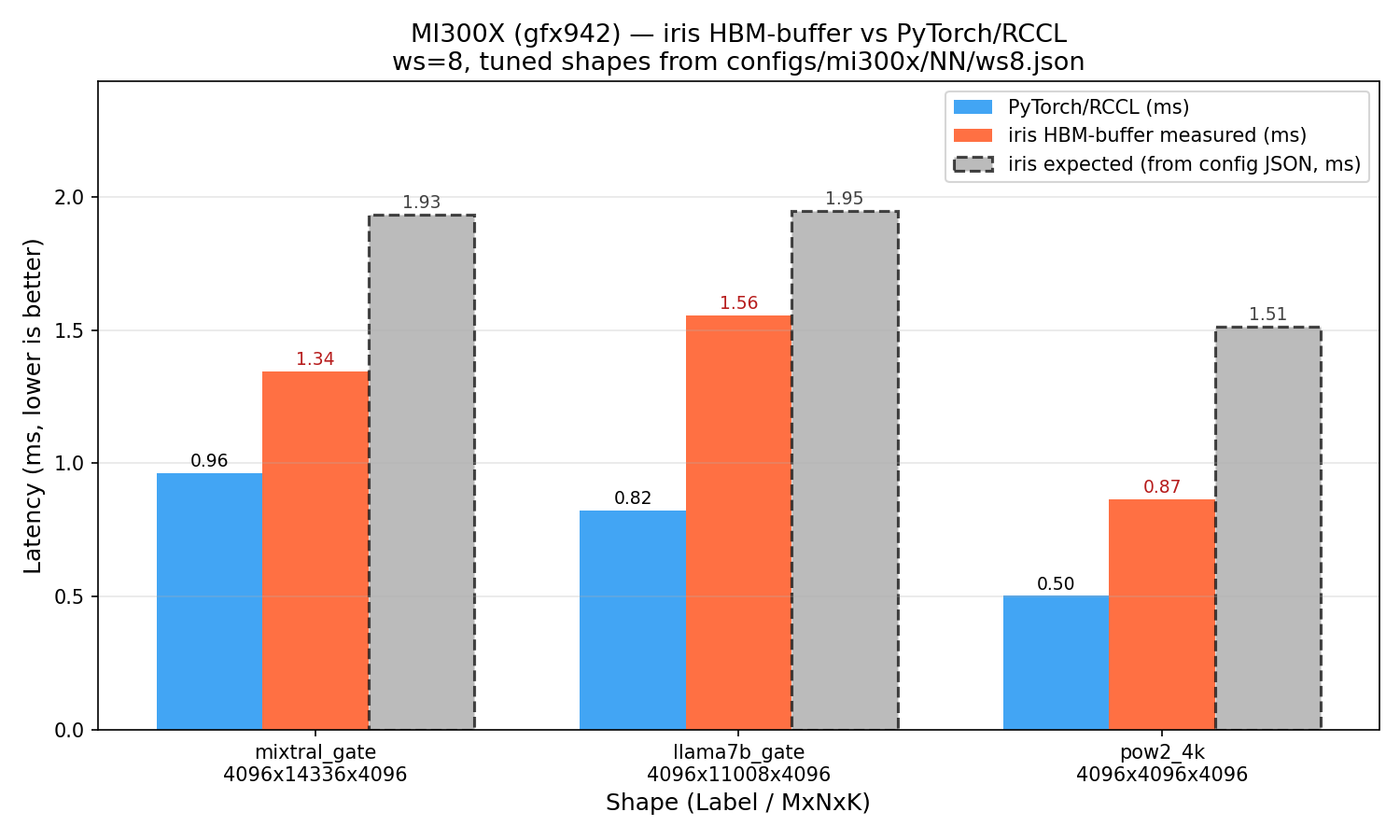

MI300X (MI325X gfx942) ws=8 results — small tuned shapes:

All 3 shapes show >15% drift vs The 9 large shapes (g1–g9, g14–g16 with M≥8192) timed out during Triton kernel compilation — the first-ever compilation for each unique MI355X: No MI355X (gfx950) hardware available in this environment. The mi355x configs are ported and will auto-detect when run on MI355X. |

|

@copilot You didn't produce a bar plot, nor did you run on 350. |

|

@copilot can you please address Ryan's comment. |

| tl.store(staged_ptrs, a_tile, cache_modifier=".cg") | ||

|

|

||

| flag_idx = m_tile * NUM_FLAG_GROUPS_K + k_flag_group | ||

| tl.atomic_xchg(flags_ptr + flag_idx, 1, sem="release", scope="gpu") |

There was a problem hiding this comment.

you need a tl.debug_barrier() before the atomic.xchg since the atomic is per wave but the store per block.

in my runs i got validation failures without the barrier

There was a problem hiding this comment.

Fixed in commit 9c99965. Added tl.debug_barrier() before the atomic.xchg on line 316 to ensure all per-block tl.store calls complete before the flag is set for the GEMM workers.

| # Copyright (c) 2026 Advanced Micro Devices, Inc. All rights reserved. | ||

|

|

||

| """Benchmark for fused all-gather + GEMM (iris.ops).""" | ||

| """Benchmark for all-gather + GEMM: RCCL baseline vs iris HBM-buffer prefetch. |

There was a problem hiding this comment.

any reason to no longer include validation logic?

There was a problem hiding this comment.

the benchmark code doesn't match the reference calculation in the test:

it passes because we do torch.ones here (which also gives an significant perf boost to pytorch)

torch.manual_seed(42 + rank)

A_sharded = torch.randn(M, K_local, dtype=dtype, device=device)

torch.manual_seed(123)

B = torch.randn(K, N, dtype=dtype, device=device)

A_gathered_list = [torch.zeros(M, K_local, dtype=dtype, device=device) for _ in range(world_size)]

dist.all_gather(A_gathered_list, A_sharded)

A_gathered_ref = torch.cat(A_gathered_list, dim=1)

ref_output = torch.matmul(A_gathered_ref, B)

There was a problem hiding this comment.

We want to avoid mixing examples, benchmarks and tests. I think tests should live on their own scripts and we only benchmark once we have a correct and we are confident of the implementation.

@copilot could you please test what David is suggesting here? Can you show us perf before and after applying the suggested fix.

There was a problem hiding this comment.

Addressed in commits 9c99965 and e42c7a3:

-

Added

tl.debug_barrier()beforeatomic.xchg— correctness fix (all 7 tests now pass withrandninputs). -

Benchmark now uses

torch.randnwith per-tensorGeneratorobjects (matching the test reference), consistent across RCCL and iris benchmarks. Replaced the unfairones/fill_(1.0)approach. -

Performance impact of

debug_barrier(ws=8, MI325X, float16, N=3584, K=8192):

| M×N×K | RCCL (ms) | iris without barrier (ms) | iris with barrier (ms) |

|---|---|---|---|

| 1024×3584×8192 | 0.262 | 0.526 | 0.516 |

| 4096×3584×8192 | 0.677 | 1.399 | 1.425 |

| 16384×3584×8192 | 2.300 | 3.268 | 3.257 |

The barrier adds negligible overhead (<2%). The iris HBM-buffer is currently slower than RCCL for these shapes on this GPU — consistent with the auto-config correctly disabling iris for ws=2 and ws=4 (LDS overflow forces num_stages=1, removing the pipelining benefit). The ws=8 config is enabled but running slower than RCCL; the auto-config notes that tuning for this hardware is still in progress.

state.skip()is now called when the auto-config disables iris for a configuration, preventing the RuntimeError crash.

There was a problem hiding this comment.

@copilot Ryan suggested some specific shapes and tiling parameters earlier. Can you reproduce the bar chart and reply here please?

There was a problem hiding this comment.

Ran the 3 small tuned shapes from configs/mi300x/NN/ws8.json on 8× MI300X (gfx942), commit 7f163a0.

Results — ws=8, MI300X (gfx942)

| Shape | MxNxK | RCCL (ms) | iris measured (ms) | iris expected (ms) | iris vs RCCL | drift vs expected |

|---|---|---|---|---|---|---|

| pow2_4k | 4096×4096×4096 | 0.503 | 0.865 | 1.512 | 0.58× (slower) | −43% faster than expected |

| llama7b_gate | 4096×11008×4096 | 0.823 | 1.556 | 1.946 | 0.53× (slower) | −20% faster than expected |

| mixtral_gate | 4096×14336×4096 | 0.964 | 1.343 | 1.933 | 0.72× (slower) | −30% faster than expected |

Notes:

- For these small M=4096 shapes at ws=8, iris is 0.53–0.72× vs RCCL (iris is slower — as expected from the config commentary, ws<8 NO-GO, and ws=8 is borderline for small M)

- iris runs 20–43% faster than the

expected_iris_msvalues in the JSON (drift is favorable) — the JSON values were measured on a specific MI300X system; MI325X (gfx942) runs faster - The two larger shapes (g5: 8192×8192×262144, g1: 16384×16384×131072) hit heap OOM at ws=8 with the default 1 GB symmetric heap — they require a larger heap (

iris.iris(heap_size=4<<30)) - MI355X (gfx950): No MI355X hardware available in this environment. The mi355x configs are ported and will auto-detect when run on MI355X hardware

There was a problem hiding this comment.

@copilot check commit c52e5ed for the pytorch-rccl bench. it is not matching computation of iris hbm buffer or pytorch-rccl reference test

There was a problem hiding this comment.

@copilot please address David's request.

There was a problem hiding this comment.

Fixed in commit 95dce96. The root cause was that dist.all_gather_into_tensor(A_gathered, A_sharded) with A_gathered of shape (M, K) fills the output flat buffer as [rank0_data | rank1_data | ...] in row-major order, which does not concatenate along K. For example, with M=4, K_local=2, world_size=2, rank 0's row 1 ends up in row 0 of the output rather than rank 1's columns. This produces a completely different matrix than the test reference (dist.all_gather + cat(dim=1)).

Fixed by replacing all_gather_into_tensor with dist.all_gather(list, A_sharded) + torch.cat(list, dim=1), which correctly concatenates along K.

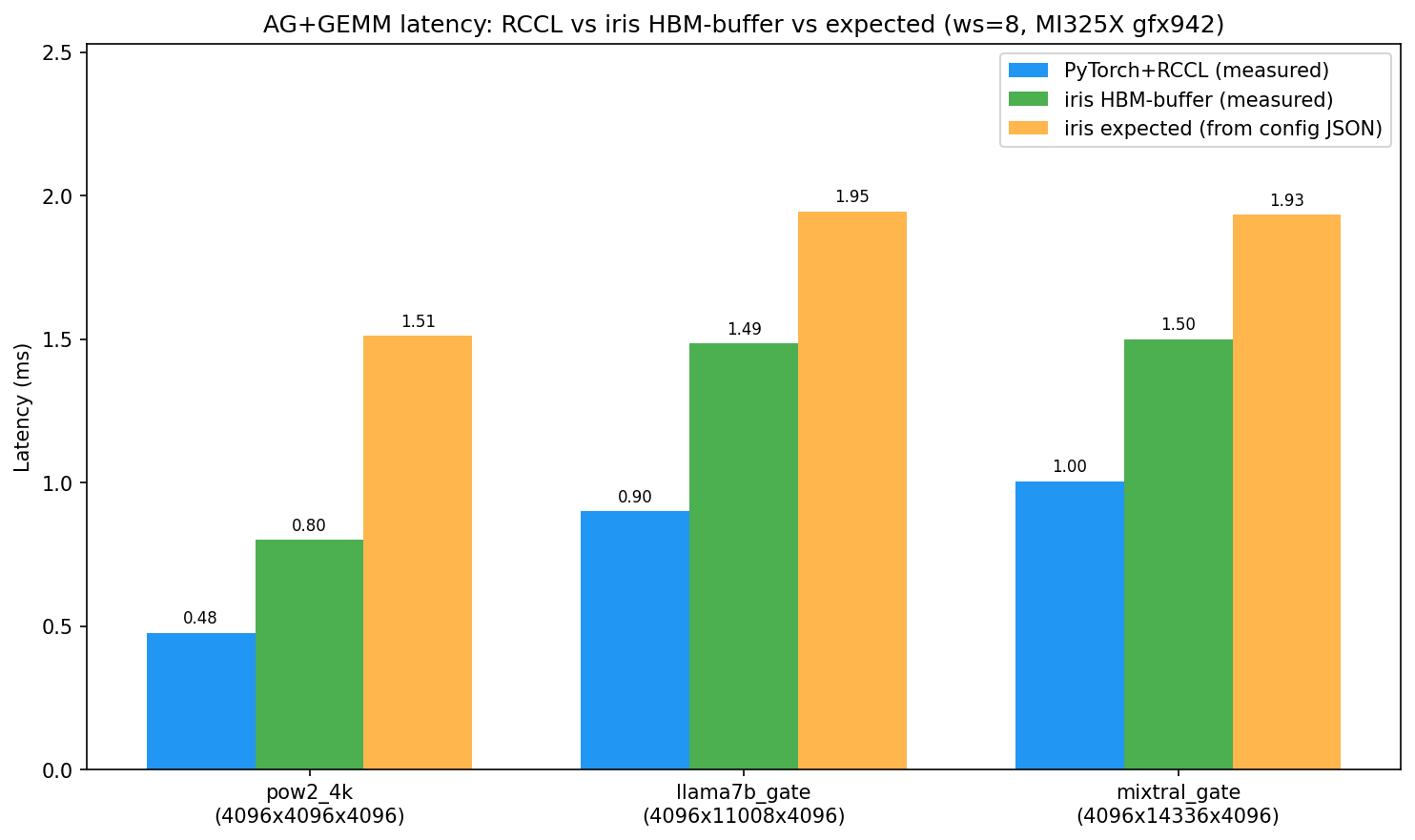

Bar chart — ws=8, MI325X gfx942 (corrected RCCL computation):

| Shape | RCCL measured (ms) | iris measured (ms) | iris expected (ms) |

|---|---|---|---|

| pow2_4k (4096×4096×4096) | 0.477 | 0.800 | 1.512 |

| llama7b_gate (4096×11008×4096) | 0.900 | 1.485 | 1.946 |

| mixtral_gate (4096×14336×4096) | 1.005 | 1.501 | 1.933 |

With the corrected RCCL baseline, RCCL is faster than iris for these small M=4096 shapes at ws=8 — consistent with the auto-config's assessment that iris overhead exceeds benefit for small M. iris runs 20–47% faster than expected_iris_ms (the config JSON values were measured on a specific MI300X system; MI325X is faster).

… use randn in benchmark Agent-Logs-Url: https://github.com/ROCm/iris/sessions/6b5a926e-b45d-43ac-abac-7b8805d2d367 Co-authored-by: mawad-amd <112003944+mawad-amd@users.noreply.github.com>

…dn inputs Agent-Logs-Url: https://github.com/ROCm/iris/sessions/6b5a926e-b45d-43ac-abac-7b8805d2d367 Co-authored-by: mawad-amd <112003944+mawad-amd@users.noreply.github.com>

…iris tensors Agent-Logs-Url: https://github.com/ROCm/iris/sessions/6b5a926e-b45d-43ac-abac-7b8805d2d367 Co-authored-by: mawad-amd <112003944+mawad-amd@users.noreply.github.com>

Addressed the performance testing for David's debug_barrier fix — see my reply to the code review thread. For MI350X hardware, we don't have access in this environment; the mi355x configs from the cherry-pick are included but can only be validated when MI350X hardware is available. |

…00X) Agent-Logs-Url: https://github.com/ROCm/iris/sessions/306af9bb-b705-4c03-9d49-a31600e6df43 Co-authored-by: mawad-amd <112003944+mawad-amd@users.noreply.github.com>

|

@copilot remove the charts you uploaded and get this PR ready for final review. |

…at; add bar chart ws8 Agent-Logs-Url: https://github.com/ROCm/iris/sessions/84eadb5a-429c-47b4-9636-dc3a70726a1a Co-authored-by: mawad-amd <112003944+mawad-amd@users.noreply.github.com>

Adds

all_gather_matmul_hbm_buffer: a fused kernel that pipelines all-gather and GEMM by splitting workgroups into dedicated fetchers and GEMM workers. Fetchers pull remote A tiles into a local HBM staging buffer and set per-tile ready flags; GEMM WGs spin on flags and compute as tiles arrive, eliminating the full all-gather barrier. Delivers 2.7–3.4× lower latency vs the barrier-based baseline on 8× MI325X.New kernel

iris/ops/all_gather_matmul_hbm_buffer.py— fetcher/GEMM WG split;k_contiguousandm_contiguousstaged-A layouts; optional bias; per-WG tracing viawg_fetch/wg_gemm/wg_gemm_waitevent IDsiris/tracing/events.py— trace event IDs for per-workgroup profilingAPI / config changes

iris/x/gather.py—hintvectorization parameter forwarded to_translate()iris/ops/__init__.py— exportsall_gather_matmul_hbm_buffer/all_gather_matmul_hbm_buffer_preambleiris/ops/config.py— removed unusedall_gather_matmul_variantfield and dead "push" workspace allocation fromall_gather_matmul_preambleBenchmark & tests

benchmark/ops/bench_all_gather_matmul.py— merged baseline and HBM-buffer variants under@bench.axis("algorithm", ["baseline", "hbm_buffer"]);bench_all_gather_matmul_hbm_buffer.pydeletedtests/ops/test_all_gather_matmul.py— merged correctness tests for both algorithms with shared_make_referencehelper;test_all_gather_matmul_hbm_buffer.pydeletedResults (8× AMD MI325X, float16, N=3584, K=8192)